New Analysis Exposes CERN’s €4 Billion FPGA Misstep and Champions Crosetto’s 3D-Flow Breakthrough

Dario Crosetto

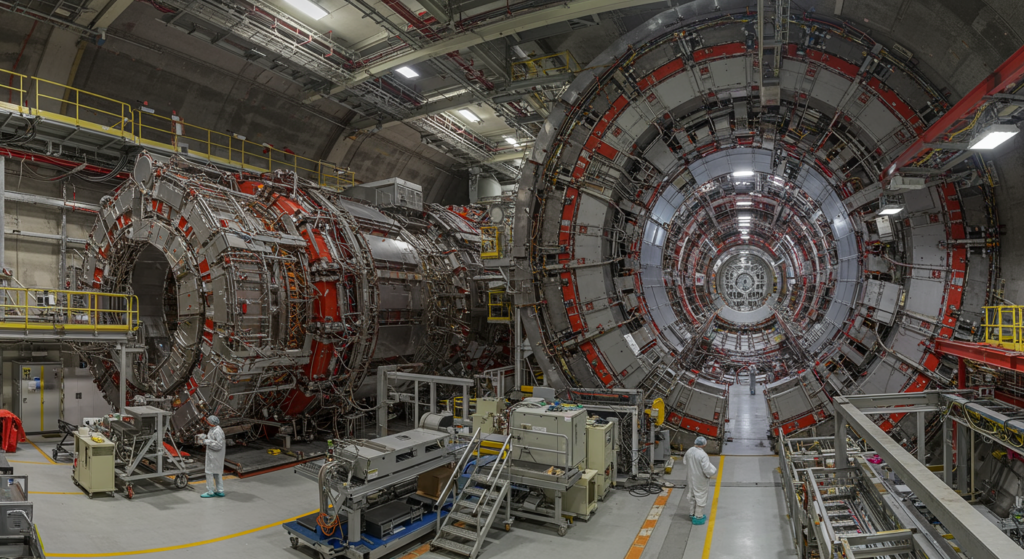

A recent 82-page study by the Crosetto Foundation reveals that CERN’s FPGA-based Level-1 Trigger architecture has consumed over €4 billion in public funds and over 650 kW of power, yet fails to match the efficiency of Dario Crosetto’s 3D-Flow system, which delivers equivalent performance using 20 billion transistors at just 6 kW and a fraction of the cost. Supported by the 2024 IEEE-NSS-MIC-RTSD Chairs, the foundation calls for an open technical debate with CERN designers to restore transparency and ensure optimal use of taxpayer investments. The report also underscores the life-saving potential of Crosetto’s technology in early cancer detection, estimating that its deployment could have saved 39 million lives worldwide.

21 May 2025: The Crosetto Foundation for the Reduction of Cancer Deaths today released “Evidence That CERN Wasted Over €4 Billion,” an 82-page scientific article demonstrating that CERN ignored Italian-American physicist Dario Crosetto’s 3D-Flow architecture for over two decades in favor of a power-hungry, inflexible FPGA-based Level-1 Trigger design.

Transparency in Science has gained momentum after the 2024 IEEE-NSS-MIC-RTSD Chairs allocated the longest presentation slot of their entire conference to Crosetto’s six accepted papers, endorsing efforts to hold major institutions accountable for public spending.

That analysis remains unrefuted by CERN, IEEE, the Pontifical Academy of Sciences or any international expert panel. It documents a €4 billion overspend at CERN and highlights how the current FPGA-based trigger—already under construction for the 2026–2036 LHC upgrade—uses 20 trillion transistors and consumes over 650 kW, yet still risks data loss during peak collision events.

Architectural Flaw of FPGA Technology

“FPGA technology, whose architecture is unsuited for Level-1 Trigger applications. FPGAs dedicate only 13% of transistors to logic, with 87% for routing interconnects and other functions. This inflates execution time, leading to missed data. Critically, attempting to compensate by instantiating multiple parallel circuits on an FPGA is counterproductive. Increasing parallelism means more transistors, which inherently increases routing delays. This necessitates even more circuit copies, creating a vicious cycle. The current CERN FPGA-based Level-1 Trigger, detailed in official reports 3 4, has reached a staggering 20 trillion transistors (see Table II) and consumes over 650 kW. Even a 100-trillion-transistor version consuming several megawatts could never offer the flexibility and efficiency of Crosetto’s system, which can handle 8,000 programmable operations per dataset arriving every 25 ns without data loss at just 6 kW, and at a fraction of the cost (see Table I and Fig. 1).”

Crosetto’s 3D-Flow architecture, first lauded as a breakthrough at Fermilab in 1993, achieves LHC trigger requirements using only 20 billion transistors—one-one-thousandth the transistor count—and draws 6 kW, making it over 100 times more efficient than CERN’s FPGA solution while meeting projected luminosity demands through 2046.

Beyond high-energy physics, Crosetto’s innovations extend to early cancer detection. His 3D-Complete Body Screening (3D-CBS) device, invented in 2000, could have saved an estimated 39 million lives worldwide by catching tumors at a curable stage, yet remains suppressed.

The foundation urges a public technical debate with CERN developers, academic bodies and policymakers to restore scientific rigor and accountability in the allocation of over €4 billion of public funds to this critical infrastructure.

Related posts